CRV - Constrained Random Verification

Weryfikacja to obecnie "wąskie gardło" w procesie projektowania. W przypadku dużych projektów ASIC czy FPGA weryfikacja to 70% całkowitego czasu poświęconego na taki projekt . Producenci narzędzi EDA (Electronic Design Automation) starają się dostarczyć nowoczesne rozwiązania, które skrócą czas weryfikacji zapewniając jednocześnie pokrycie całej funkcjonalności projektu wyczerpującymi testami. Testy bazujące na pseudo losowym generowaniu wymuszeń były stosowane od dawna w rożnych dziedzinach a zwłaszcza w telekomunikacji. Ostatnio pojawiły się jednak języki i narzędzia, które zapewniają stosunkowe szybkie i proste tworzenie testów opartych o generacje pseudo losową. W literaturze stosuje się nazwę Constrained Random Verification w odniesieniu do tej dziedziny weryfikacji. Na rynku możemy odnaleźć kilka rozwiązań wspomagających weryfikacje oparta o generacje losowe:

-

SystemC SCV - darmowa biblioteka w C++ dostarczająca niezbędne klasy do budowy testów z generacją pseudo losową.

-

SystemVerilog - to nowy język będący rozszerzeniem języka Verilog-HDL. Nowe możliwości tego języka umożliwiają weryfikację z generacją pseudo losową. Jest dostarczany w narzędziach takich firm jak Aldec, Mentor Graphics czy Synopsys.

-

SpecMan eTM - to nowy język dostarczany przez firmę Cadence. Różni się znacząco od dotychczasowych rozwiązań gdyż jest językiem aspektowo orientowanym.

-

VeraTM - język dostarczany przez firmę Synopsys. Jest językiem o składni zbliżonej do C++. Czyli generalnie jest to język obiektowo orientowany.

Trudno określić, które z tych rozwiązań jest najlepsze. Ale SystemVerilog będący rozszerzeniem popularnego języka Verilog-HDL wydaje się mieć duże szanse na rozpowszechnienie. Należy również dodać, że od 2007 roku planuje się rozpoczęcie prac nad rozszerzeniem języka VHDL o konstrukcje umożliwiające generacje pseudo losowe.

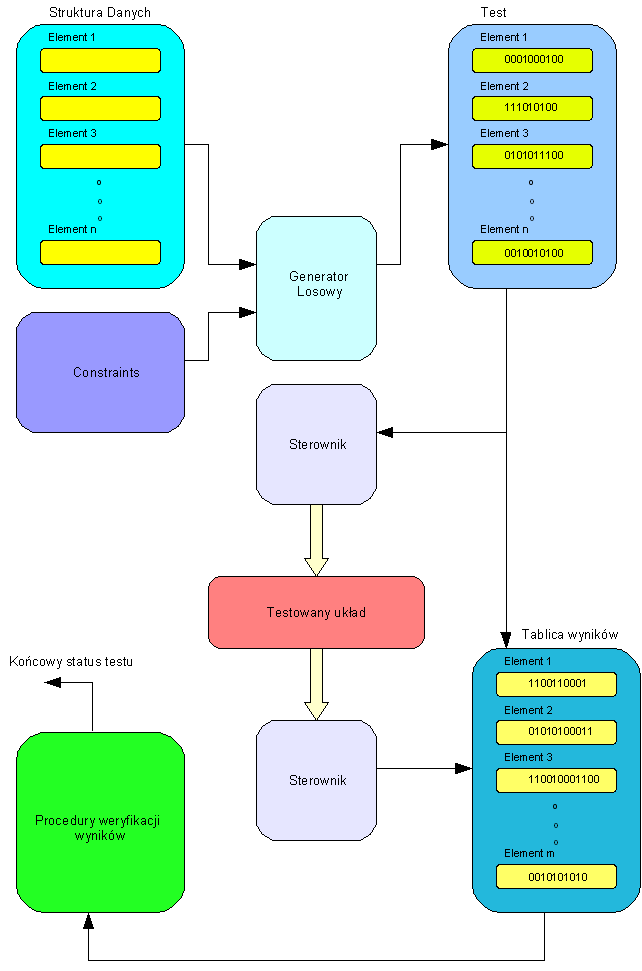

Architektura testbench'a z generacją pseudo losową jest we wszystkich przypadkach stosunkowo podobna. Użytkownik musi zdefiniować strukturę lub struktury danych odpowiadające wymuszeniom, które można przyłożyć do testowanego układu. Następnie definiowane są tzw. constraints czyli ograniczenia dla generatora losowego. Zawartość struktur danych jest generowana losowo. Jednak każde losowanie musi wygenerować ważne i legalne wymuszenie dla testowanego układu. Nie można generować wymuszeń, które są nielegalne z punktu widzenia specyfikacji testowanego układu. Constraints służą do sterowania generacja losowa w taki sposób aby generowane wymuszenia były zgodne ze specyfikacją.

|

Następny element takiego testbench'a to sterownik, który przykłada wymuszenia do portów testowanego modułu zgodnie z protokołem jego interfejsu. Sterownik to zwykle funkcjonalny model interfejsu testowanego modułu. Pobiera on strukturę danych z generatora i steruje testowany moduł generując odpowiednie cykle akceptowane przez jego interfejs. Przykładowo cykle zapisu dla magistrali AMBA AHB. Liczbę przyłożonych testów definiujemy przez liczbę losowań. Tutaj widać przewagę testbench'a z generacją losową nad testbench'em z bezpośrednimi wymuszeniami. W przypadku testbench'a z bezpośrednimi wymuszeniami mamy do dyspozycji tylko te wymuszenia, które bezpośrednio zapisaliśmy. Podczas gdy generacja losowa zapewnia dowolną liczbę wymuszeń a także różne sekwencje tych wymuszeń, które zwykle wykraczają daleko poza wyobraźnie projektantów i inżynierów weryfikacji. Aby zapewnić odpowiednie pokrycie testami, wystarczy prawidłowo zapisać constraints i zapewnić odpowiednią liczbę losowań. Należy tutaj dodać, że większość narzędzi zapewnia mechanizmy do sprawdzania czy cały kod testowanego układu został odpowiednio pobudzony. Jeżeli tak nie jest to należy zmienić constraints. Możliwe jest również automatyczne adaptacyjne zmienianie constraints aby osiągnąć wyczerpujące pobudzenia dla testowanego układu. Aczkolwiek jest to zagadnienie stosunkowo trudne do realizacji w przypadku dużych projektów.

Generacja wymuszeń jest stosunkowo prosta ale weryfikacja odpowiedzi nastręcza sporo trudności we wszystkich narzędziach. Odpowiedzi są odczytywane z testowanego układu przy pomocy podobnego lub nawet tego samego sterownika, który był używany do przykładania wymuszeń. Sterownik zapisuje odpowiedzi do osobnych struktur danych. Tworząc w ten sposób tablice wyników. Do weryfikacji wyników musimy niestety napisać odpowiednie funkcje. Są one często podobne do funkcji znajdujących się testowanym układzie. Inżynierowie weryfikacji poświęcają na ten element testbench'a znacznie więcej czasu niż na generator wymuszeń. Ale w testbench'ach z bezpośrednim wymuszeniami sytuacja jest podobna z tym, ze generator wymuszeń nastręczą równie dużo trudności. Zatem testbench'e z generacją losową są o wiele wydajniejsze skracając znacząco czas poswięcony na tworzenie testów i zapewniając dokładniejszą weryfikacje.

|